(→Protokoll: zomg Datenrate) |

(→Protokoll: Mehr details + Beispiellink) |

||

| Line 17: | Line 17: | ||

== Protokoll == | == Protokoll == | ||

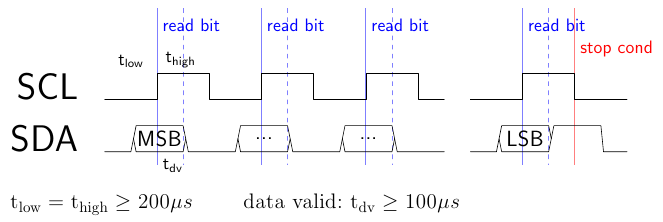

Bitbasiert, | Bitbasiert. Im Ruhezustand sind SDA und SCL low, die erste steigende SCL-Flanke ist auch das erste most significant bit der Übertragung (es gibt keine start condition). Bei jeder weiteren steigenden SCL-Flanke werden weitere Bits eingelesen, beendet wird das ganze durch die stop condition: Fallende SCL-Flanke mit SDA high. D.h.: Falls weitere bits folgen, muss SDA vor der fallenden SCL-Flanke auf low gesetzt werden. | ||

Auf höherer Ebene gilt: Es können beliebig viele Bits / Bytes übertragen werden, solange die least significant (d.h. die letzten) 16 Bit die Geräteadresse sind. Nach einer steigenden SCL-Flanke ist das SDA-Signal für 1µs gültig, d.h. es muss in dieser Zeit eingelesen und verarbeitet werden. Die Low- bzw. High-Phase von SCL dauert je 2µs, nach der stop condition darf beliebig lange nicht auf den Bus reagiert werden. For the record: Die Übertragungsrate ist damit 250kbit/s. | |||

=== TLDR === | |||

{| class="wikitable" | {| class="wikitable" | ||

| Line 31: | Line 33: | ||

|} | |} | ||

[[Image:SI2C-Timing.png]] | |||

AVR-C-Beispiel: [https://github.com/derf/dorfmap/blob/master/avrshift/main.c#L68 avrshift/main.c Z.68ff] | |||

== Kabel == | == Kabel == | ||

Revision as of 22:07, 24 August 2013

| Vereinfachtes I²C | |

|---|---|

| Einwege-Kommunikation | |

| Ort | Hauptraum |

| Besitzstatus | Club-Eigentum |

| Kontakt | derf |

| Benutzung | vorsichtig |

I²C-basierte twowire-Verbindung, aktuell writeonly.

Hardware

TBD. Auf dem Endgerät sollten SDA und SCL per Optokoppler galvanisch getrennt sein und Spannungen im Bereich 3 .. 16 Volt akzeptieren.

Protokoll

Bitbasiert. Im Ruhezustand sind SDA und SCL low, die erste steigende SCL-Flanke ist auch das erste most significant bit der Übertragung (es gibt keine start condition). Bei jeder weiteren steigenden SCL-Flanke werden weitere Bits eingelesen, beendet wird das ganze durch die stop condition: Fallende SCL-Flanke mit SDA high. D.h.: Falls weitere bits folgen, muss SDA vor der fallenden SCL-Flanke auf low gesetzt werden.

Auf höherer Ebene gilt: Es können beliebig viele Bits / Bytes übertragen werden, solange die least significant (d.h. die letzten) 16 Bit die Geräteadresse sind. Nach einer steigenden SCL-Flanke ist das SDA-Signal für 1µs gültig, d.h. es muss in dieser Zeit eingelesen und verarbeitet werden. Die Low- bzw. High-Phase von SCL dauert je 2µs, nach der stop condition darf beliebig lange nicht auf den Bus reagiert werden. For the record: Die Übertragungsrate ist damit 250kbit/s.

TLDR

| SCL | SDA | Aktion |

|---|---|---|

| ↑ | X | Bit X von rechts (als Least Significant Bit) ins Register schieben |

| ↓ | 1 | stop condition: Eingabedaten übernehmen |

| ↓ | 0 | Keine |

AVR-C-Beispiel: avrshift/main.c Z.68ff

Kabel

| Bus | Kabel |

|---|---|

| feedback1 | Schleuse an feedback |

| donationprint1 | Schleuse an donationprint |

| donationprint2 | Schleuse donationprint |

Pinbelegung 4pol-Flachbandkabel

- 1: SDA

- 2: VCC (9V .. 12V)

- 3: GND

- 4: SCL

Pinbelegung 8pol-Flachbandkabel

Geplant, für Kombikabel mit CAN und SI2C.

- 1: CANH

- 2: 12V

- 3: CANL

- 4: GND

- 5: SDA

- 6: GND

- 7: SCL

- 8: 5V

Devices

Soft- und Firmware liegen aktuell im dorfmap-Repo.

| Bus | ID | Firmware rev | Funktion |

|---|---|---|---|

| feedback1 | 0002 | 0.04-42-g1a373d3 | avrshift (serial in, parallel 12V out als current sink) |

| feedback1 | 0004 | 0.04-106-g544d694 | 7segment Hackcenter (8 Ziffern, links) |

| feedback1 | 0005 | 0.04-106-g544d694 | 7segment Hackcenter (8 Ziffern, rechts) |

| feedback1 | 0006 | 0.04-120-gf2b7838 | avrmf mit parallel 5V out (5 digital, 3 pwm) |

| donationprint1 | 0000 | 0.04-42-g1a373d3 | avrshift (serial in, parallel 12V out als current sink) |

| donationprint2 | 0001 | 0.04-110-gfa20b4e | blinkencontrol (RGB) |

| donationprint2 | 0003 | 0.04-50-gf6641aa | 7segment Lounge (4 Ziffern) |